# 1.8 V Current & Voltage Reference

**Product Brief**

### **Product Overview**

DARE22G IVREF18 implements a bandgap-based reference voltage and current generator for radiation-hardened applications in the commercial GF 22 nm FDSOI CMOS technology.

This IP macro supports a range of DARE22G platform IP blocks that require on-chip current and/or voltage biasing, such as LVDS, BBG, and OSC100M.

## **Features**

Main functionalities include:

- 0.6 V and 1.25 V (±1%) reference voltages

- 10 µA high-accuracy current sources (10 replicas)

- 10 μA internal biasing current sources for external reference voltage generation (9 replicas)

- Excellent stability over supply voltage, load variation and temperature

- Low operating current (< 420 μA)</li>

- Digital calibration

- Power-down mode (< I μA)</li>

- TID immunity over 100 krad (SiO<sub>2</sub>)

- SET immunity over 60 MeV.cm<sup>2</sup>/mg

- SEL immunity over 70 MeV.cm<sup>2</sup>/mg

# **Block Diagram**

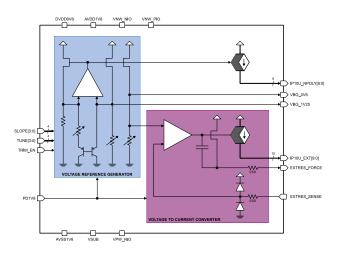

The IVREF18 macro comprises a bandgap circuit, current mirrors, and a voltage-to-current converter. The bandgap circuit generates 0.6 V and 1.25 V reference voltage signals which are output through the VBG\_0V6 and VBG\_IV25 pins, respectively. Digital calibration for voltage offset and temperature drift can be performed using trimming codes provided via the TUNE[3:0] and SLOPE[3:0] input buses. Calibration is enabled when the TRIM\_EN input is asserted during start-up.

The voltage-to-current converter uses internal reference voltage signals to generate high-accuracy 10  $\mu A$  current source replicas, which are output via the IP10U\_EXT[9:0] bus. This functionality requires an external pull-down resistor connected to both EXTRES\_FORCE and EXTRES\_SENSE pins. Additionally, integrated current mirrors replicate the internal bandgap biasing current to deliver several 10  $\mu A$  biasing current sources via the IP10U\_NPOLY[8:0] output bus.

High-accuracy current sources are designed for general applications and rely on an accurate external resistor, which is usually practical only off-chip. In contrast, internal biasing current sources offer a fully integrated alternative that requires no external components. These current sources are more sensitive to PVT variations but can be paired with dedicated NPOLY resistors to create accurate reference voltage signals in external circuits.

Output current source replicas allow multiple blocks to be biased from a single IVREF18 instance.

## Pin Interface

| Pin Name                                | Туре    | Description                                |  |  |

|-----------------------------------------|---------|--------------------------------------------|--|--|

| AVDD1V8                                 |         |                                            |  |  |

|                                         | Power   | Analog power supply                        |  |  |

| DVDD0V8                                 | Power   | Digital power supply                       |  |  |

| AVSS1V8                                 | Ground  | Ground supply                              |  |  |

| VSUB                                    | Ground  | P-substrate bias voltage                   |  |  |

| VNW_PIO                                 | Power   | Back-bias voltage for reversed-biased NMOS |  |  |

| VNW_NIO                                 | Power   | Back-bias voltage for forward-biased NMOS  |  |  |

| VPW_NIO                                 | Ground  | Back-bias voltage for reversed-biased PMOS |  |  |

| VBG_0V6                                 | Analog  | 0.6 V reference voltage                    |  |  |

| VBG IV25                                | Analog  | 1.25 V reference voltage                   |  |  |

| IPI0U_NPOLY[8:0]                        | Analog  | 10 μA internal biasing                     |  |  |

|                                         | ŭ       | current sources                            |  |  |

| IP10U_EXT[9:0]                          | Analog  | 10 μA high-accuracy                        |  |  |

|                                         | Ü       | current sources                            |  |  |

| EXTRES FORCE                            | Analog  | External 12 kΩ resistor                    |  |  |

| _                                       | Ü       | low-ohmic connection                       |  |  |

| EXTRES SENSE                            | Analog  | External 12 kΩ resistor                    |  |  |

| · <u>-</u> -                            |         | sensing connection                         |  |  |

| PD1V8                                   | Digital | Power-down enable                          |  |  |

| TUNE[3:0]                               | Digital | Offset trimming bits for                   |  |  |

|                                         | - 10    | reference voltages                         |  |  |

| SLOPE[3:0]                              | Digital | Temperature slope                          |  |  |

| []                                      | 0       | trimming bits for                          |  |  |

|                                         |         | reference voltages                         |  |  |

| TRIM EN                                 | Digital | Trimming enable                            |  |  |

| - · · · · · · · · · · · · · · · · · · · | 6       |                                            |  |  |

# **Physical Dimensions**

DARE22G IVREF18 is implemented as a core macro.

| IP Name | Width  | Height |  |  |

|---------|--------|--------|--|--|

| IVREF18 | 526 µm | 220 µm |  |  |

#### **Contact**

For further information, please contact us at <a href="mailto:dare@imec.be">dare@imec.be</a>

# **Operating Conditions**

Performance and reliability are not guaranteed outside these recommended operating boundaries.

| Parameter              | Name                  | Minimum | Typical | Maximum | Unit                     |

|------------------------|-----------------------|---------|---------|---------|--------------------------|

| Digital supply voltage | $V_{\text{DD0V8}}$    | 0.72    | 0.8     | 0.88    | ٧                        |

| Analog supply voltage  | $V_{\text{DDIV8}}$    | 1.62    | 1.8     | 1.98    | V                        |

| Operating temperature  | Tj                    | -40     | 25      | 125     | °C                       |

| ESD rating (HBM)       | $V_{HBM}$             | 2       |         |         | kV                       |

| TID threshold          | $TID_th$              | 100     |         |         | krad (SiO <sub>2</sub> ) |

| LET threshold (SET)    | $LET_{th\_SET}$       | 60      |         |         | MeV.cm <sup>2</sup> /mg  |

| LET threshold (SEL)    | LET <sub>th_SEL</sub> | 70      |         |         | MeV.cm <sup>2</sup> /mg  |